Correção de erro de encaminhamento (FEC) e taxa de erro de bit (BER)

As interfaces de rede de transporte óptico (OTN) usam a taxa de erro de correção de erro pré-encaminhamento (pré-FEC) de bits (BER) para monitorar a condição de um link OTN. Use este tópico para entender mais sobre como os links OTN são monitorados e os modos FEC suportados nos dispositivos.

Visão geral

Interfaces ópticas na Série PTX suportam o monitoramento da condição de um link óptico usando a taxa de erro de erro pré-encaminhamento (pré-FEC). Os PICs a seguir oferecem suporte ao monitoramento pré-FEC BER:

P1-PTX-2-100G-WDM

P2-100GE-OTN

P1-PTX-24-10G-W-SFPP

Os PICs usam correção de erro de encaminhamento (FEC) para corrigir erros de bits nos dados recebidos. Enquanto o PRÉ-FEC BER estiver abaixo do limite da FEC, todos os erros de bits são identificados e corrigidos com sucesso e, portanto, nenhuma perda de pacote ocorre. O sistema monitora o PRÉ-FEC BER em cada porta. Isso dá um aviso antecipado da degradação do enlace. Ao configurar um limiar e intervalo PRÉ-FEC DENS apropriados, você permite que o PIC tome medidas preventivas antes que o limite de FEC seja atingido. Se você combinar a lógica de limiar DER pré-FEC com o redirecionamento rápido do MPLS, então você pode evitar ou minimizar a perda de pacotes.

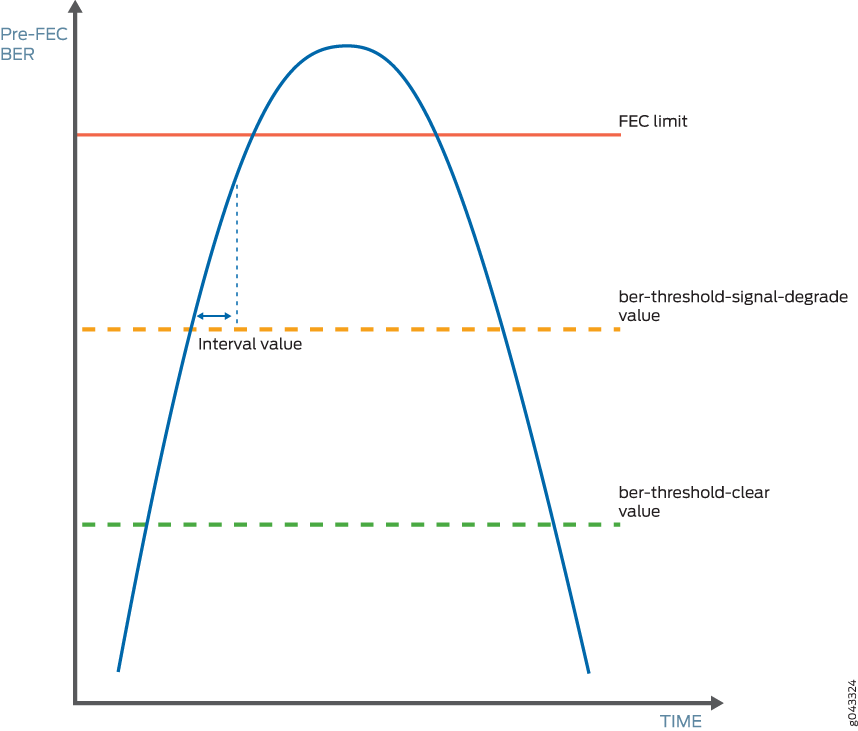

Você deve especificar tanto o limiar de degradação de sinal (degradado por um limiar de sinal) quanto o intervalo (intervalo) para a interface. O limiar define os critérios DENS para uma condição de degradação de sinal e o intervalo define a duração mínima sobre a qual o BER deve exceder o limite antes que um alarme seja levantado. A relação entre o limiar e o intervalo é ilustrada em Figura 1. Depois que um alarme é levantado, se o BER retornar a um nível abaixo do valor claro do limiar (sem limite máximo), o alarme será liberado.

Com o monitoramento PRÉ-FEC BER habilitado, quando o limiar de degradação do sinal PRÉ-FEC BER configurado é atingido, o PIC para de encaminhar pacotes para a interface remota e aumenta o alarme da interface. Os pacotes de entrada continuam a ser processados. Se o monitoramento PRÉ-FEC BER for usado com o redirecionamento rápido do MPLS ou outro método de proteção de enlaces, o tráfego será redirecionado para uma interface diferente.

Você também pode configurar o redirecionamento rápido para trás para inserir o status local pré-FEC em quadros ópticos transmitidos, notificando a interface remota de degradação do sinal. A interface remota pode usar as informações para redirecionar o tráfego para uma interface diferente. Se você usar o monitoramento DER pré-FEC em conjunto com o redirecionamento rápido para trás, então a notificação da degradação do sinal e do redirecionamento do tráfego ocorre em menos tempo do que o necessário por meio de um protocolo de Camada 3.

Inclua as signal-degrade-monitor-enable declarações e backward-frr-enable declarações no nível de hierarquia para permitir o [edit interfaces interface-name otn-options preemptive-fast-reroute] monitoramento pré-FEC BER e o redirecionamento rápido para trás.

Quando você configura o monitoramento degradado do sinal PRÉ-FEC BER, recomendamos que você configure as declarações e as signal-degrade-monitor-enablebackward-frr-enable declarações.

Você também pode configurar os limiares DESAS pré-FEC que levantam ou limpam um alarme degradante de sinal e o intervalo de tempo para os limiares. Se os limiares e o intervalo DENP não estiverem configurados, os valores padrão serão usados.

Quando um alarme degradado por sinal recebido é ativado e o redirecionamento rápido para trás é habilitado, uma bandeira específica é inserida na sobrecarga de óptica trasmitida. O PIC remoto na extremidade oposta do link monitora a sobrecarga óptica, permitindo assim que ambas as extremidades iniciem o redirecionamento de tráfego em caso de degradação de sinal. Quando a condição de degradação do sinal é limpa, a bandeira aérea é devolvida a um estado normal.

O valor limite de degradação do sinal PRÉ-FEC DEGRADE define uma quantidade específica de margem do sistema em relação ao limite de correção DESP (ou limite FEC) do decodificador FEC recebido do PIC. Cada PIC tem um limite fec definido — é intrínseco à implementação do decodificador FEC.

Os exemplos abaixo usam medições de fator Q2 (também conhecidas como fator Q). O fatorQ 2 é expresso em unidades de decibéis em relação a um fator Q2 de zero (dBQ). O fatorQ 2 permite que você descreva a margem do sistema em termos lineares em contraste com os valores DANS, que são de natureza não linear. Depois de determinar os limiares, você deve converter os valores limiares do fator2º trimestre para o BER para inseri-los na CLI usando notação científica. O BER pode ser convertido ao fatorQ 2 usando a seguinte equação:

Q2-factor = 20 * log10 (sqrt(2) * erfcinv(2 * BER))

Para converter entre o fatorQ 2 e o BER em um programa de planilha, você pode aproximar os valores usando as seguintes fórmulas:

Para calcularo fator 2º trimestre:

= 20 * LOG10(–NORMSINV(BER))

Para calcular o BER:

= 1 – NORMSDIST(10^(0.05 * Q2-factor))

Inclua a ber-threshold-signal-degrade, ber-threshold-cleare interval as declarações no nível de [edit interfaces interface-name otn-options signal-degrade] hierarquia para configurar os limiares DENS e o intervalo de tempo.

Configurar um alto limiar DENS para degradação de sinal e um longo intervalo pode fazer com que o contador interno fique saturado. Essa configuração é ignorada pelo roteador, e os valores padrão são usados. Uma mensagem de log do sistema está registrada para este erro.

Valores de degradação de sinal e limite claro para PICs

Tabela 1 mostra a relação entre o limite fixo de FEC, o limiar de degradação do sinal configurável e o limiar claro configurável para diferentes PICs. Neste exemplo, aproximadamente 1 dBQ de margem de sistema foi definida entre o limite da FEC, o limiar de degradação do sinal e o limiar claro.

|

PIC |

Tipo FEC |

Limite da FEC |

Limiar de degradação de sinal |

Limite claro |

|||

|---|---|---|---|---|---|---|---|

| Fator2 Q | BER | Fator2 Q | BER | Fator2 Q | BER | ||

|

P1-PTX-2-100G-WDM |

SD-FEC |

6,7 dBQ |

1.5E–2 |

7,7 dBQ |

7.5E–3 |

8,7 dBQ |

3.0E–3 |

|

P2-100GE-OTN |

G.709 GFEC |

11,5 dBQ |

8.0E–5 |

12,5 dBQ |

1.1E–5 |

13,5 dBQ |

1.0E–6 |

|

P1-PTX-24-10G-W-SFPP |

G.975.1 I.4 (UFEC) |

9,1 dBQ |

2.2E–3 |

10,1 dBQ |

6.9E–4 |

11,1 dBQ |

1.6E–4 |

|

G.975.1 I.7 (EFEC) |

9,6 dBQ |

1.3E–3 |

10,6 dBQ |

3.6E–4 |

11,6 dBQ |

7.5E–5 |

|

|

G.709 GFEC |

11,5 dBQ |

8.0E–5 |

12,5 dBQ |

1,1E–5 |

13,5 dBQ |

1,0E–6 |

|

Para ajustar o limiar de degradação do sinal, você deve primeiro decidir sobre uma nova meta de margem do sistema e, em seguida, calcular o respectivo valor DESAS (usando a equação para converter do fator Q2 para o BER). Tabela 2 mostra os valores se 3 dBQ de margem de sistema em relação ao limite da FEC forem necessários para que o limite de degradação do sinal (mantendo o limiar claro em 1 dBQ em relação ao limiar de degradação do sinal).

A escolha da margem do sistema é subjetiva, pois você pode querer otimizar seus limites com base em diferentes características de enlace, tolerância a falhas e objetivos de estabilidade. Para obter orientações sobre a configuração do monitoramento pré-FEC BER e dos limiares DENS, entre em contato com seu representante da Juniper Networks.

|

PIC |

Tipo FEC |

Limite da FEC |

Limiar de degradação de sinal |

Limite claro |

|||

|---|---|---|---|---|---|---|---|

| Fator2 Q | BER | Fator2 Q | BER | Fator2 Q | BER | ||

|

P1-PTX-2-100G-WDM |

SD-FEC |

6,7 dBQ |

1,5E–2 |

9,7 dBQ |

1.1E–3 |

10,7 dBQ |

2.9E–4 |

|

P2-100GE-OTN |

G.709 GFEC |

11,5 dBQ |

8.0E–5 |

14,5 dBQ |

4.9E–8 |

15,5 dBQ |

1.1E–9 |

|

P1-PTX-24-10G-W-SFPP |

G.975.1 I.4 (UFEC) |

9,1 dBQ |

2.2E-3 |

12,1 dBQ |

2.8E–5 |

13,1 dBQ |

3.1E–6 |

|

G.975.1 I.7 (EFEC) |

9,6 dBQ |

1,3E–3 |

12,6 dBQ |

1,1E–5 |

13,6 dBQ |

9.1E–7 |

|

|

G.709 GFEC |

11,5 dBQ |

8.0E–5 |

14,5 dBQ |

4.8E–8 |

15,5 dBQ |

1,1E–9 |

|

Modos de correção de erro para o futuro suportados

Esta seção descreve os modos FEC suportados em diferentes roteadores no [edit interfaces interface-name otn-options] nível.

Roteadores da série MX

|

Placa de linha |

Modo FEC |

Velocidade de porta |

|---|---|---|

|

|

10G |

|

|

|

10G e 100G (apenas GFEC) |

|

|

|

10G |

|

|

|

100G (apenas GFEC) |

|

|

|

100G |

Roteadores da série PTX

|

Placa de linha |

Modo FEC | Velocidade de porta |

|---|---|---|

| P1-PTX-24-10G-W-SFPP |

(gfec | efec | nenhum | ufec) |

10G |

| P2-10G-40G-QSFPP |

(gfec | efec | nenhum | ufec) |

10G |

| P2-100GE-OTN |

(gfec | nenhum) |

100G (apenas GFEC) |

| P1-PTX-2-100G-WDM |

(gfec-sdfec) |

100G |

| PTX-5-100G-WDM |

(gfec | sdfec) |

100G |

Consulte também

Modos de correção de erro avançados suportados em roteadores da Série PTX

Tabela 6 lista os modos FEC que são suportados em roteadores da Série PTX no nível de [edit interfaces interface-name otn-options] hierarquia.

Placa de linha |

Modo FEC |

Velocidade de porta |

Versão junos |

|---|---|---|---|

|

10G |

12,1X48, 12,3, 13,2 (PTX5000)13.2R2 (PTX3000) |

|

|

10G |

14.1R2 (PTX5000)15.1F6 (PTX3000) |

|

|

100G (apenas GFEC) |

14.1 |

|

|

100G |

13,2 (PTX5000)13,3 (PTX3000) |

|

|

100G |

15.1F6 |

Consulte também

Modos de correção de erro para o futuro suportados no roteador ACX6360

Tabela 7 lista os modos FEC que são suportados em roteadores ACX6360 no nível hierárquicos [edit interfaces interface-name optics-options] .

Modo FEC |

Formato de modulação |

Velocidade de porta |

Versão junos |

|---|---|---|---|

|

QPSK |

100G |

18.3R1 |

|

QPSK |

100G |

18.3R1 |

|

8-QAM |

200G |

18.3R1 |

|

16-QAM |

200G |

18.3R1 |

Consulte também

Modos FEC suportados no roteador ACX5448-D

Tabela 8 lista os modos de correção de erro (FEC) que são suportados em roteadores ACX5448 D. Você pode configurar os modos FEC no nível de [edit interfaces interface-name optics-options] hierarquia.

Modo FEC |

Formato de modulação |

Velocidade de porta |

Junos OS |

|---|---|---|---|

|

QPSK |

100 Gbps |

19.2R1-S1 |

|

QPSK |

100 Gbps |

19.2R1-S1 |

|

QPSK |

100 Gbps |

19.2R1-S1 |

|

8-QAM |

200 Gbps |

19.2R1-S1 |

|

16-QAM |

200 Gbps |

19.2R1-S1 |

Consulte também

Tabela de histórico de alterações

A compatibillidadde com o recurso dependerá da platadorma e versão utilizada. Use o Feature Explorer para saber se o recurso é compatível com sua plataforma.